~1桁ナノメートル領域にてAIから⾞載まで利用可能に~

不揮発性メモリ(電源を切っても情報が保持されるメモリ)は半導体の大幅な省エネ化をもたらすと期待されており、人工知能(AI)、もののインターネット(IoT)から車載まで幅広いアプリケーションでの利用に向けて研究開発が進められています。特にスピントロニクス(注2)技術を利用したスピン移行トルク磁気抵抗メモリ(STT-MRAM)は、大手半導体デバイスメーカーから1Xナノメートル世代(注3)の車載向け半導体への導入が発表されるなど注目を集めています。より微細化が進んだ将来の半導体回路で幅広いアプリケーションに対応するためには、STT-MRAMの記憶素子である磁気トンネル接合(MTJ)素子そのものの微細化とともに、アプリケーション毎で異なる高速性や高温でのデータ保持特性などの要求性能を満たしていく必要があります。

今回、東北大学電気通信研究所の五十嵐純太学術研究員(当時)、同大学材料科学高等研究所(WPI-AIMR)の陣内佛霖助教(当時)、深見俊輔教授、大野英男教授(現総長)らは、直径一桁ナノメートル領域で様々なアプリケーションの要求性能に応じてカスタマイズできる磁気トンネル接合(MTJ)素子(注4)を提案し、その材料・構造の設計指針を体系化しました。MTJにCoFeB/MgO材料系からなる積層磁性層構造を導入し、その膜厚や積層回数を変化させて、車載応用に必要な高温での高いデータ保持特性やAI/IoT用途で求められる高速でのデータ書き込み特性を直径一桁ナノメートルの極微細領域でそれぞれ満たすことができることを実証しました。

これは、STT-MRAMが将来の極微細世代の半導体技術にて幅広い用途に展開可能であることを示す重要な成果です。また本研究で提案した構造は、大手半導体デバイスメーカーの既存設備により形成可能であり、今後のSTT-MRAMのスケーリングを支え、社会実装範囲を拡大する基盤となることが期待されます。

本研究成果は、2024年1月4日(英国時間)に論文誌npj Spintronicsに掲載されました。

半導体集積回路の大幅な低消費電力化をもたらすと期待されている不揮発性メモリ(電源を切っても情報が保持されるメモリ)の研究開発が、AI/IoTから車載まで幅広いアプリケーションでの利用に向けて進められています。

車載応用では比較的高温での長期データ保持特性が必要となり、これまで埋め込みフラッシュメモリが用いられていましたが、微細化限界のためそれに代わる新しい技術での置き換えが求められていました。スピントロニクスに基づくスピン移行トルク磁気抵抗メモリ(STT-MRAM)は、それに応える技術として1X ナノメートル世代の車載向け半導体集積回路への導入が大手半導体デバイスメーカーから発表され、今後の益々の発展に向け注目を集めています。

一方で、AI/IoT用途では高速性や高い書き換え耐性が重視されます。現状はその高い要求のため実績豊富な揮発性メモリであるSRAMやDRAMが利用されていますが、省エネ化のためにはそれに取って代わることのできる不揮発性メモリが必要であり、ここでもSTT-MRAMが有力候補と目されています。

現在埋め込みフラッシュ置き換えとして製品化が進められているSTT-MRAMにおいては、データの記憶を担う磁気トンネル接合(MTJ)素子の記憶層にはコバルト鉄ホウ素(CoFeB)層が酸化マグネシウム(MgO)層で挟まれた構造が用いられています。素子のデータ保持特性は垂直磁気異方性と素子サイズに依存し、この構造にて1Xナノメートル世代の車載向け半導体集積回路で要求されるデータ保持特性が満たされています。

東北大学の研究グループは、CoFeB/MgO界面由来の垂直磁気異方性を用いた素子(2010年)ならびに二重界面構造の開発(2012年)と、現在の世界標準であるMTJ素子技術の確立に大きく貢献してきました。しかし、さらに微細化が進む将来のXナノメートル・オングストローム世代(注3)の半導体集積回路で用いられるサイズのMTJ素子では、現行技術で車載応用やAI/IoT向けアプリケーションの要求性能を満たすことは困難であり、新たなブレイクスルーが求められていました。

MTJ素子の更なる微細化を実現するため、同グループは2018年に素子を縦長に形成(膜厚を直径よりも大きく設定)することで垂直方向の形状磁気異方性を利用できることを示し [東北大学プレスリリース『磁気トンネル接合素子、未踏の一桁ナノメートル領域で動作実現』](注5)、2020年には世界最小直径2.3ナノメートルのMTJ素子で将来世代での車載応用が視野に入る、高温での高いデータ保持特性を実証しました [東北大学プレスリリース『世界最小磁気トンネル接合素子の高性能動作を実証』](注6)。さらに2021年に直径一桁ナノメートル(直径5ナノメートル以下)の極微細領域でCoFeB/MgO界面を六重や八重にすることで、数ナノ秒の高速動作が可能であることを示しました [東北大学プレスリリース『オングストローム世代半導体製造技術での磁気抵抗メモリ基盤技術を確立』](注7)。このように形状磁気異方性と界面磁気異方性を利用したMTJ素子の高性能動作への道筋が見え始めたことを受け、将来の幅広いアプリケーションの要求性能を満たす、界面・形状磁気異方性を利用した極微細領域のMTJ素子の体系的な設計指針を確立することが求められていました。

今回、研究グループは、現在主流となっているCoFeB/MgO材料系を変えることなく、直径一桁ナノメートルのMTJ素子を、幅広い用途で要求される性能に応じてカスタマイズする材料・構造技術を体系的に明らかにしました。

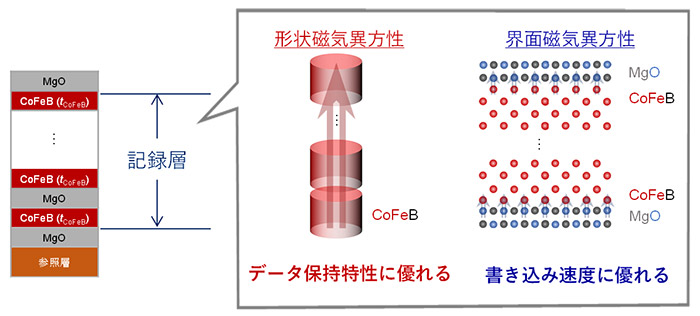

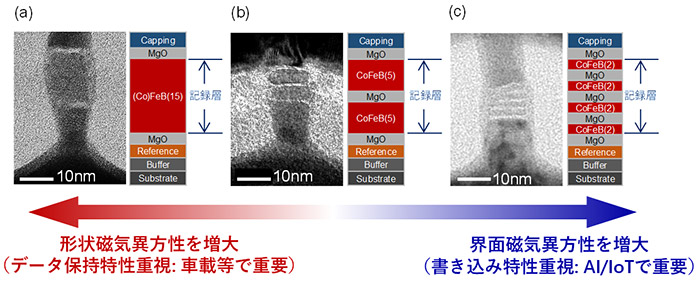

本研究で提案した構造が図1に示されています。CoFeB/MgOからなる積層磁性層構造のCoFeB層の膜厚とMgO挿入層の数(積層回数)を変化させることで、界面異方性と形状異方性を独立に制御できます[図1]。CoFeB層膜厚を直径に対して厚くして形状磁気異方性が支配的に作用するように設計された構造は、高温でのデータ保持特性に優れます[図2(a), (b)]。一方、CoFeB層を薄くしつつ積層回数を増やし、界面磁気異方性が支配的に作用するように設計された構造は高速書き込み性に優れます[図2(c)]。

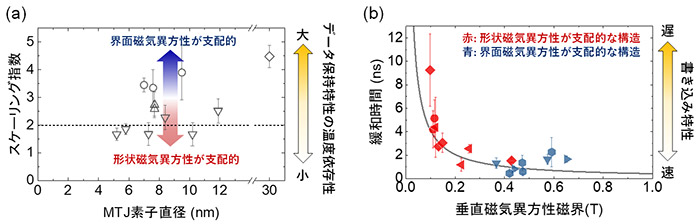

図3には本研究で作製したMTJ素子でのデータ保持特性および書き込み特性の評価結果が示されています。形状磁気異方性が支配的な構造ほど、データ保持特性の温度依存性を特徴づけるスケーリング指数が小さくなっています[図3(a)]。これはデータ保持特性の温度依存性が小さくなっていることを示しており、形状磁気異方性が支配的な構造が、高温での長期データ保持が求められる車載向けのアプリケーションに適していることを意味します。実際に作製した直径7.6ナノメートルの素子にて、150℃での十分に高いデータ保持特性が確認されました。一方、書き込み速度は緩和時間と呼ばれる時定数で特徴づけられ、緩和時間が短いほど高速での書き込みが可能です。界面磁気異方性が支配的な構造ほど、短い緩和時間が得られており[図3(b)]、高速な書き込みが可能、すなわちAI/IoTなどのアプリケーションに適していることを意味しています。実際に作製した直径4.5ナノメートルの素子にて、比較的高いデータ保持特性を示しながら、1ボルト以下、10ナノ秒の電圧パルスでデータ書き換えができることが確認されました。また、材料・構造を変えることにより、1ボルト以下、1ナノ秒の電圧パルスでのデータ書き換えが実現可能であることを計算により予測しました。

本研究により、極微細MTJ素子において所望な特性を得るための材料・構造技術とその物理的理解が形成され、今後STT-MRAMが幅広いアプリケーションに展開されるための基盤的理解が構築されました。また今回開発した積層磁性層構造は、現在主流のCoFeB/MgO材料で実現できるため、大手半導体デバイスメーカーの既存設備で製造可能です。そのため本研究で得られた成果は、幅広いアプリケーションでの将来の極微細世代半導体集積回路に向けたSTT-MRAM開発を加速するものと期待されます。

図1. 本研究で提案した積層磁性層構造。データ保持特性を重視する場合、CoFeB層膜厚を厚くし、CoFeB/MgO層の積層回数を少なくすることで形状磁気異方性の割合を増やす。書き込み速度を重視する場合、CoFeB層膜厚を薄くし、CoFeB/MgO層の積層回数を増やすことで界面磁気異方性の割合を増やす。

図2. 本研究で作製した積層磁性層構造を有するMTJ素子の透過型電子顕微鏡(TEM)とその膜構造の模式図。

図3. 本研究で作製したMTJ素子に対して行った、(a) データ保持特性の温度依存性を特徴づけるスケーリング指数、(b) 高速性を特徴づける緩和時間の測定結果。(a)の破線は形状磁気異方性のみを考慮した場合のスケーリング指数の理論値。(b)の曲線は理論式によるフィッティング結果。

本研究は日本学術振興会科学研究費助成事業(JP19K04486, JP19J12926)、科学技術振興機構(JST)産学共創プラットフォーム共同研究推進プログラム(OPERA)「世界の知を呼び込むIT・輸送システム融合型エレクトロニクス技術の創出」(領域統括 東北大学 遠藤哲郎)、東北大学スピントロニクス国際共同大学院などの支援の下で行われたものです。本研究のMTJ素子のすべての作製工程は、東北大学電気通信研究所附属ナノ・スピン実験施設にて同グループが有する微細加工技術を駆使して行われました。

| タイトル: | “Single-nanometer CoFeB/MgO magnetic tunnel junctions with high-retention and high-speed capabilities” (高い情報保持特性と高速動作を実現可能な一桁ナノメートルCoFeB/MgO磁気トンネル接合) |

|---|---|

| 著者: | Junta Igarashi*, Butsurin Jinnai*,**, Kyota Watanabe, Takanobu Shinoda, Takuya Funatsu, Hideo Sato, Shunsuke Fukami**, and Hideo Ohno * 共同筆頭著者 ** 責任著者: 東北大学材料科学高等研究所・助教(当時)・陣内 佛霖 東北大学電気通信研究所・教授・深見 俊輔 |

| 雑誌名: | npj Spintronics |

| DOI番号: | 10.1038/s44306-023-00003-2 |

東北大学電気通信研究所

(兼)東北大学先端スピントロニクス研究開発センター (CSIS)

(兼)東北大学国際集積エレクトロニクス研究開発センター (CIES)

(兼)東北大学材料科学高等研究所 (WPI-AIMR)

(兼)稲盛科学研究機構 (InaRIS)

教授 深見 俊輔

| Tel: | 022-217-5555 |

|---|---|

| E-mail: | s-fukami@tohoku.ac.jp |

東北大学電気通信研究所 総務係

| Tel: | 022-217-5420 |

|---|---|

| E-mail: | riec-somu@grp.tohoku.ac.jp |