~現行AIの計算方式に対応したスピントロニクス『P』コンピュータの動作を実証~

人工知能(AI)やデジタル社会の進展に伴い、コンピュータで処理するタスクは複雑かつ多様化しています。この要請に応えるため、各用途に特化した新概念コンピュータの研究開発が活性化しています。

スピントロニクス確率論的(『P』)コンピュータは確率性を伴う複雑な問題を省電力で超高速に処理できると期待される新概念コンピュータの一種です。東北大学とカリフォルニア大学サンタバーバラ校(アメリカ)のチームは以前から共同研究を行っており、昨年実験結果に基づき汎用的なコンピュータと比べて演算速度を約5桁向上、消費電力を約1桁低減できることを示していました。一方で昨今急成長するAI技術への応用に向けては、現行AIの大部分が採用する計算方式である順伝播型ニューラルネットワーク[図1]に整合した技術の開発が求められていました。

今回研究チームはスピントロニクスPコンピュータにて順伝播型ニューラルネットワークに基づく計算を行うための新技術を開発し、行動履歴や生活習慣と病気の発症の因果関係を確率的に解析するAI計算のデモ実験などに成功しました。また併せて、これまでのPコンピュータの動作速度を3桁向上する新素子技術を開発しました。

AIの更なる発展に向けてはコンピュータの演算能力の向上と省エネ化の両立が喫緊の課題となっています。スピントロニクスPコンピュータはまさにこの要請に応えるものであり、本研究にて現行AIと高い整合性を有した技術が確立されたことから、今後社会実装に向けた研究開発がより一層進展するものと期待されます。

本成果は、2023年12月9-13日(米国時間)に米サンフランシスコで開催される学術会議「International Electron Devices Meeting: IEDM」で発表されました。

AI(人工知能)は言うまでもなく現代の社会基盤の一つであり、直近では生成AIの出現が社会に様々な革新をもたらそうとしています。一方でAIの発展はコンピュータの演算能力に過剰な要求を突き付けてもいます。コンピュータの演算能力は1960年頃から約50年にわたって、ほぼ1.5年ごとに2倍のペースで向上してきました(ムーアの法則)が、2010年以降はこれを5倍以上上回るペース(1年で約10倍)でAI計算量が増加しています。このようなAI計算量の増大はデータセンターでの電力消費を3倍増加させているとも言われており、持続可能な社会の実現を目指す以上、看過できない懸案でもあります。この問題に対処するためには、AI計算を超低電力で行える革新的なコンピューティング技術の導入が不可欠です。特にコンピュータに求められるタスクが多様化する昨今、全てに対処し得る万能コンピュータの実現を期待することは非現実的であり、各用途に特化した様々なコンピュータ(Domain-specific computer)を開発して使い分けていくことが有効と考えられています。

複雑な問題(例えば気象予測など)を処理するソフトウェア技術としてしばしば乱数アルゴリズムが用いられています。これは特に確率性を伴う事象を扱うのに適していますが、現行の決定論的に動作するコンピュータとは本質的には相性が悪く、計算に多大な電力が費やされています。この問題を解決する手法の一つとして、1981年にアメリカの物理学者リチャード・ファインマン博士は、ハードウェアのレベルで確率論的に振る舞うコンピュータ(確率論的(Probabilistic)コンピュータ = Pコンピュータ)の可能性に言及しました。しかしそれから約40年の間、Pコンピュータを実現するための有効策は明らかではありませんでした。

2019年に東北大学とパデュー大学(アメリカ)の共同研究にて、自然の熱で確率的に状態が更新されるスピントロニクス素子を用いたPコンピュータのデモシステムが構築され、複雑性の高い問題の典型例である組合せ最適化の原理実証が行われました(東北大学プレスリリース 『室温動作スピントロニクス素子を用いて量子アニーリングマシンの機能を実現』(注3))。また、2022年には東北大学とカリフォルニア大学サンタバーバラ校(アメリカ)の共同研究にて、実験結果に基づいたPコンピュータの性能予測から、従来型の決定論的に動作する汎用コンピュータと比べて、Pコンピュータは乱数アルゴリズムを用いた計算の速度を約5桁、消費電力を1桁改善できることが示されていました(東北大学プレスリリース『確率動作スピン素子を用いた高性能・省電力「P」コンピューターを実証』(注4))。

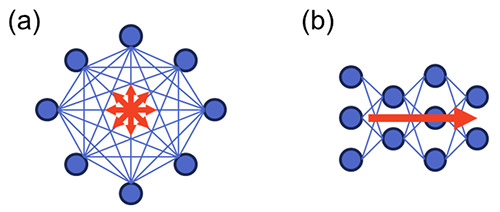

一方で、スピントロニクスPコンピュータを社会で広く用いられているAI技術に適用するためには一つの障壁がありました。それはAI計算とこれまでのスピントロニクスPコンピュータの間での数学的な計算モデル(ニューラルネットワークの種類)の違いに関係します。図1に代表的なニューラルネットワークである再帰型ニューラルネットワーク(Recurrent Neural Network)と順伝播型ニューラルネットワーク(Feed-forward Neural Network)の構造を示しました。再帰型ニューラルネットワーク(図1(a))では、ノード間での情報の行き来の方向が定まっていない(例えばノードAはノードBに影響を与え、同時にノードBはノードAに影響を与える)のに対して、順伝播型ニューラルネットワーク(図1(b))はノードからノードへと情報が流れる方向が定まっています。順伝播型ニューラルネットワークは現行の逐次的に演算を行うコンピュータとの相性が良くほぼ全てのAIで用いられているのに対して、これまでに開発されたPコンピュータの演算では再帰型ニューラルネットワークが用いられていました。すなわち、順伝播型ニューラルネットワークに対応したスピントロニクスPコンピュータを実現できれば、現在汎用コンピュータを用いて行われているAI処理をそのままスピントロニクスPコンピュータにてより高速にかつ低い電力で実行でき、それを契機にその後はPコンピュータの特徴を活かした様々なアプリケーションが開拓されていくものと期待されます。

今回、東北大学の金子遥南氏(大学院生・工学研究科)、金井駿准教授(電気通信研究所)、大野英男教授(現総長)、深見俊輔教授(電気通信研究所)らは、カリフォルニア大学サンタバーバラ校のKerem Camsari博士らのチームと共同で、スピントロニクスPコンピュータを順伝播型ニューラルネットワークに適応させる新技術を開発し、その基本動作を実証しました。

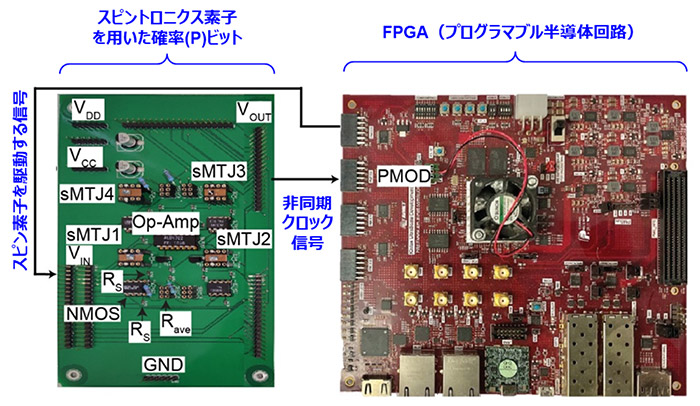

図2に構築したスピントロニクスPコンピュータの原理実証システムの写真が示されています。システムは4つの確率動作スピントロニクス素子を搭載した確率ビット(Probabilistic bit: Pビット)(注2)のユニット(左側)と、プログラマブル半導体(Field-Programmable Gate Array: FPGA)(注5)(右側)から構成されています。FPGAはどのスピントロニクスPビットを動作させるか指定し、指定されたスピントロニクスPビットは物理乱数を生成してFPGAを駆動する、という手順を繰り返すことで演算が行われるよう設計されています。

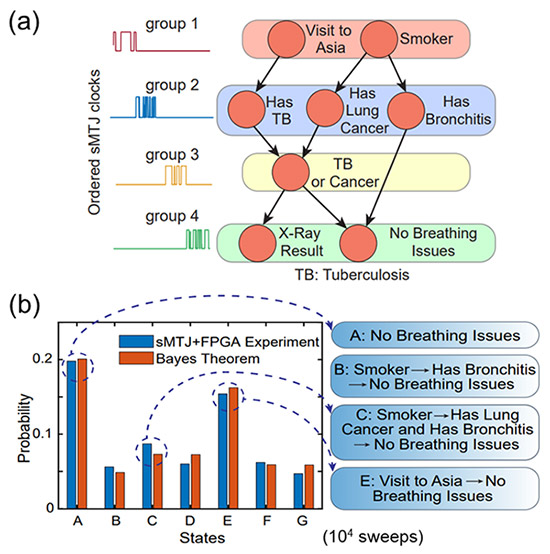

このシステムを用い、順伝播型ニューラルネットワークの一種であるベイジアンネットワーク(注6)の動作実証を行いました。図3にその結果の一例が示されています。これは1980年代に提唱された「アジアネットワーク」と呼ばれるベイジアンネットワークの教科書的な例題であり(S. L. Lauritzen and D. J. Spiegelhalter, J. R. Stat. Soc., B: Stat. 50, 157-224 (1988))、アジアへの旅行歴や喫煙習慣の有無とX線検査での異常や呼吸器系の障害の有無の間の因果関係を表したものです。図3(a)に示されるように、ベイジアンネットワークを構成する4層を4つのスピントロニクスPビットで順次更新する手順を10,000回繰り返し、各事象のセットの起こりやすさを計算しました。図3(b)はその結果です。実験結果(青の棒グラフ)はベイズの定理から予測される理想分布(赤の棒グラフ)と酷似した分布となっており、これはスピントロニクスPコンピュータが期待通りの動作をしていることを意味しています。

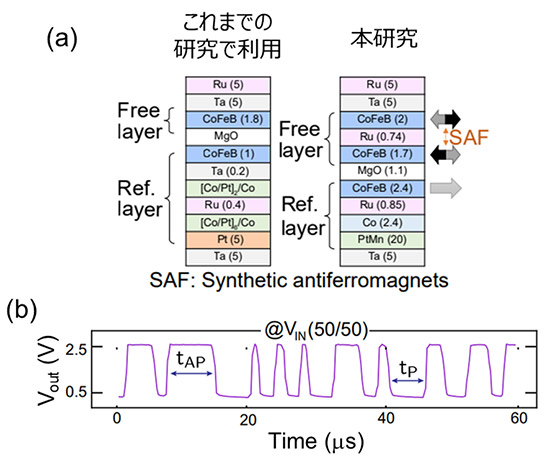

また今回の実験では、スピントロニクスPビットの素子にも工夫が施されています。一般にPコンピュータの性能はPビットの乱数生成の速度で決定され、速ければ速いほど高速での演算が可能となります。図4(a)にはこれまでの研究と今回の研究で用いられた確率動作スピントロニクス素子の膜構成が示されています。今回の研究では、これまでの東北大学の研究成果に基づき、コバルト鉄ホウ素(CoFeB)とルテニウム(Ru)が積層された構造(CoFeB/Ru/CoFeB)が用いられました。これによって外乱磁界に対する頑強さと、高速での乱数生成が実現されています。従来の構成ではミリ秒の時間スケールで乱数生成が可能であったのに対し、図4(b)に示されているように本研究で用いたPビットはマイクロ秒(0.001ミリ秒)で物理乱数を生成しています。なお東北大学のチームはさらに2桁以上速い10ナノ秒(0.01マイクロ秒)以下で乱数を生成する素子技術も確立しており(東北大学プレスリリース『スピントロニクス疑似量子ビットを従来比100倍超に高速化』(注7))、今後の更なる高速化の余力を残しています。

本研究により、これまで再帰型ニューラルネットワークの動作実証に限られていたスピントロニクスPコンピュータが、順伝播型ニューラルネットワークにも対応できることが明らかになりました。先述の通り、順伝播型ニューラルネットワークは、現行のAIの大部分が採用する計算モデルです。特に今回動作実証されたベイジアンネットワークは、複雑な事象が絡み合う一連のプロセスを解析するのに適しており、気象予測や病気の原因の推定、故障診断、マーケティングなどで広く利用されています。現在これらの計算はスーパーコンピュータ(スパコン)などの汎用性の高いハードウェアで比較的大きな電力を用いて実行されていますが、本研究によりスピントロニクスPコンピュータを用いてこれらの計算を超低電力で行う道筋が開かれました。すなわち今回開発された技術はスピントロニクスPコンピュータの社会実装の扉を開く鍵となり、それを皮切りにしてPコンピュータの特徴を活かした様々なアプリケーションが開拓されていくことが期待されます。

今後のAIの発展に向けては、コンピュータの演算能力の更なる向上と省電力化の両立が求められています。一方、スピントロニクスPコンピュータは従来型の決定論的かつ逐次的な動作を基本とするコンピュータと比べて演算能力と省エネ性を劇的に向上しうるポテンシャルを有しています。すなわち本研究成果はまさに社会的要請に応えるものであると言え、今後大規模化、集積化に向けた研究開発が進展し、利便性とエネルギー効率の高い社会の実現に向けて利用されていくことが期待されます。

図1. 再帰型ニューラルネットワーク(Recurrent Neural Network)(a)と、順伝播型ニューラルネットワーク(Feed-forward Neural Network)(b)の模式図。再帰型ニューラルネットワークは情報が双方向に流れるのに対して、順伝播型ニューラルネットワークは情報が流れる方向が規定されている。順伝播型ニューラルネットワークは現行の決定論的かつ逐次的に動作するコンピュータと相性が良く、大部分のAI処理において利用されている。

図2. 作製したスピントロニクスPコンピュータの原理実証システムの写真。左側は確率動作スピントロニクス素子からなるPビットのユニットであり、右側はプログラマブル半導体回路(FPGA)。

図3. ベイジアンネットワークの構成、スピントロニクスPビットからの出力信号(a)と、実験結果(b)。

図4. 従来研究を3桁上回る高速乱数生成動作が可能なスピントロニクス素子の膜構成(aの右側)と、今回作製したPビットが生成するランダムテレグラフノイズの測定結果(b)。

本研究は、科学技術振興機構(JST) 世界のトップ研究者ネットワーク参画のための国際研究協力プログラム(AdCORP) 「スピントロニクス確率論的コンピュータの大規模化に向けた材料・素子・回路・アルゴリズム融合研究」(研究代表者:深見 俊輔)JPMJKB2305、戦略的創造研究推進事業 CREST「スピンエッジコンピューティングハードウェア基盤」(研究代表者:佐藤 茂雄)JPMJCR19K3、および同事業さきがけ「不確定性スピントロニクス素子」(研究代表者:金井 駿)JPMJPR21B2、などの支援を受けて行われたものです。

| タイトル: | “Hardware Demonstration of Feedforward Stochastic Neural Networks with Fast MTJ-based p-bits” (高速磁気トンネル磁気トンネル接合からなる確率ビットを用いた順伝播型確率的ニューラルネットワークのハードウェア実証) |

|---|---|

| 著者: | Nihal Sanjay Singh, Shaila Niazi, Shuvro Chowdhury, Kemal Selcuk, Haruna Kaneko, Keito Kobayashi, Shun Kanai, Hideo Ohno, Shunsuke Fukami and Kerem Y. Camsari *責任著者:カリフォルニア大学サンタバーバラ校 Kerem Camsari |

| Conference: | 69th Annual IEEE International Electron Devices Meeting (IEDM 2023) |

東北大学電気通信研究所

教授 深見 俊輔

(兼)東北大学先端スピントロニクス研究開発センター (CSIS)

(兼)東北大学国際集積エレクトロニクス研究開発センター (CIES)

(兼)東北大学材料科学高等研究所 (WPI-AIMR)

(兼)稲盛科学研究機構 (InaRIS)

| Tel: | 022-217-5555 |

|---|---|

| E-mail: | s-fukami@tohoku.ac.jp |

東北大学電気通信研究所 総務係

| Tel: | 022-217-5420 |

|---|---|

| E-mail: | riec-somu@grp.tohoku.ac.jp |

科学技術振興機構 広報課

| Tel: | 03-5214-8404 |

|---|---|

| E-mail: | jstkoho@jst.go.jp |

科学技術振興機構 国際部

佐藤 正樹

| Tel: | 03-5214-7375 |

|---|---|

| E-mail: | adcorp@jst.go.jp |